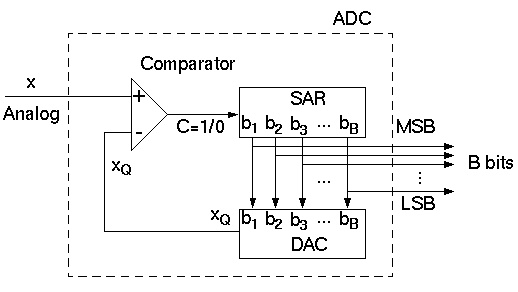

SUCCESSIVE APPROXIMATION CONVERTERS

All bits are initially cleared to zero. The successive approximation

register (SAR) tests each bit and stores a one or zero depending

on the result. The SAR leaves that bit at that level; the DAC

reconstructs the corresponding amplitude level and subtracts it

from the input signal. The process is then repeated until

all bits calculated.

C becomes a serial representation of the bit vector b.