## Name:

| Problem | Points | Score |

|---------|--------|-------|

| 1a      | 10     |       |

| 1b      | 10     |       |

| 1c      | 10     |       |

| 1d      | 10     |       |

| 2a      | 10     |       |

| 2b      | 10     |       |

| 2c      | 10     |       |

| 3a      | 10     |       |

| 3b      | 10     |       |

| 3c      | 10     |       |

| Total   | 100    |       |

## Notes:

- 1. The exam is closed book / closed notes. Students are allowed a copy sheet only **one** side of **one** standard US-size (8.5" x 11") sheet of paper on which they can write relevant information such as theorems.

- 2. Please show ALL work. Incorrect answers with no supporting explanations or work will be given no partial credit.

- 3. If I can't read or follow your solution, it is wrong, and no partial credit will be given PLEASE BE NEAT!

- 4. Please indicate clearly your answer to every problem.

- 5. There is sufficient space after each problem to write your solution. In case you need extra paper please see the instructor.

- 6. Calculators of any kind are not allowed.

## **Problem No. 1:**

An alarm system is designed to trigger on iff the number of unsuccessful password entries is 5 or more. An iterative sequential network is used to keep track of the entries, where every cell of the network records one password entry. An unsuccessful attempt is input as  $X_i = 1$ , a successful attempt is input as  $X_i = 0$ . The alarm is turned on when the final output of the network is  $Z_n = 1$ .

a) Draw the state graph of a Moore network to implement a typical cell of the iterative network. Draw the corresponding state table.

**b)** Use the implication chart method to identify equivalent states. Remove redundant states and draw the minimum state table.

**c)** Using the three guidelines for state assignment, assign the states in an optimal fashion.

d) Draw the K-maps and derive the equations for a typical cell for the alarm system.

**Problem No. 2:**

The 74S163 4-bit synchronous counter has the following function table —

| Control Signals |      | Next State |                   |                  |         |             |

|-----------------|------|------------|-------------------|------------------|---------|-------------|

| CLEAR           | LOAD | PT         | Q <sub>D</sub> +  | $Q_C^+$          | $Q_B^+$ | $Q_A^+$     |

| 0               | Х    | Х          | 0                 | 0                | 0       | 0           |

| 1               | 0    | Χ          | D <sub>D</sub>    | $D_C$            | $D_B$   | $D_A$ $Q_A$ |

| 1               | 1    | 0          | $Q_D$             | $Q_{\mathbb{C}}$ | $Q_{B}$ | $Q_A$       |

| 1               | 1    | 1          | present state + 1 |                  |         |             |

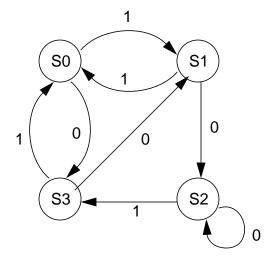

The network described by the adjacent state graph is to be implemented using a 74S163 counter and external logic gates.

a) Draw the next-state table to derive the counter inputs to implement the adjacent state graph.

**b)** Draw the K-maps and derive equations for the counter inputs.

c) Draw the network diagram with the 74163 counter chip and the external logic gates to realize the network. Use only NAND gates for the realization of external logic.

## **Problem No. 3:**

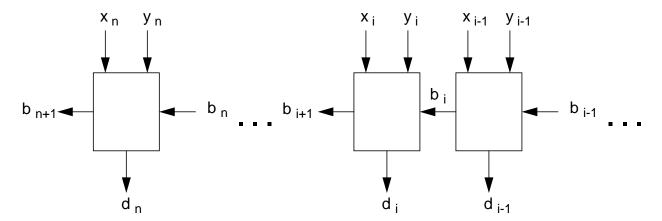

Design a full subtracter as an iterative network. This network directly subtracts one n-bit binary number from the other, as displayed in the following diagram.

The  $i^{th}$  cell implements  $d_i = x_i - y_i - b_i$  with  $b_{i+1}$  as the borrow to be propagated to the next cell.

a) Derive the truth table for a typical cell for the direct full subtracter described above.

b) Draw the K-maps and derive equations for the design of a typical cell.

c) Describe how you will use the direct full subtracter described above if 2's complement logic is used to describe negative numbers.